『FA

用語辞典』によれば「

1つの処理装

置において、2つ以上の処理を時間的にずらせて(時分割して)交互遂行させる技法。」

とあります。

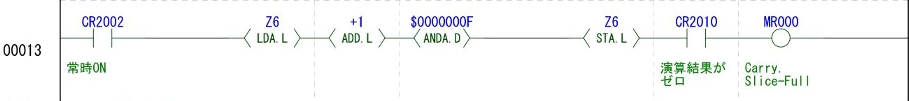

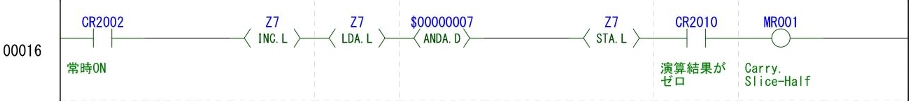

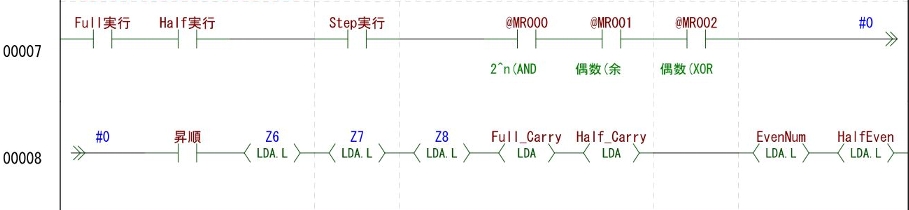

ここでは、インデックスレジスタ [Z6] / [Z7] / [Z8] でリングカウンタを作り、1スキャン毎にカウンタ値を進めています。

各モジュールでは、このインデックスレジスタを使って同様の処理を複数記述する事なく実現できます。

リングカウンタの実現方法として3種類(

2のn乗-1でマスクする

/

割算のあまりを使う /

排他的論理和で一致をみる

)挙げています。

それらをパラメータで選択でき、またステップ実行などもできます。

各カウンタの内容は、Z6

= 0 ⇒ 15 / Z7

= 0⇒ 7 / Z8

= 8 ⇒ 15 (または 15 ⇒ 8 選択可能)です。

使用例として、基本編の『仮想 エアシリンダ』

『仮想 IAIロボット』、応用編の『IAIポイント移動』

などがあるので参照してください。

・リングカウンタ値は0〜(2のn乗 − 1)

このルーチンを使うには [@MR000]をセットしてください。

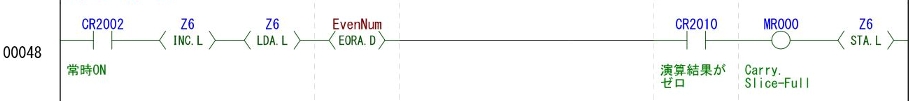

・[Z6]に「1」を加えて F(hex)と論理積をとります。

・F(hex)は2進で(1111) なので、Z6が0〜15(dec)〔0000〜1111(bin)〕の時は変化しません。

しかし、Z6が16(dec)〔10000(bin)〕 になると、Z6は0に戻ります。

・これを再度[Z6]に戻します。その結果、[Z6] は 0〜15 を繰り返します。

・この時、[Z6]が0なら桁上フラグ[MR000]を立てます。

・余談ですが、ここで[Z6]をインクリメントする方法として、四則演算の「加算」を使っています。

下の[Z7]はインクリメント命令を使っています。

KV-3000の実行時間では<ADD.L>が0.02μ秒、<INC.L>は0.13μ秒な ので、加算命令の方が早い事がわかります。

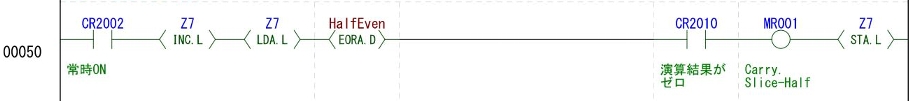

・同様に[Z7]をインクリメントして7(hex)との論理積をとって再度[Z7]に戻します。その結果、[Z7]は 0〜7 を繰り返します。

・桁上があると[MR001]を立てます。

・[Z7]は[Z6]が1巡する間、2回桁上します。

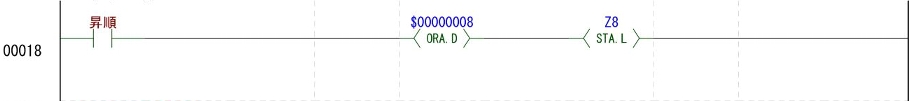

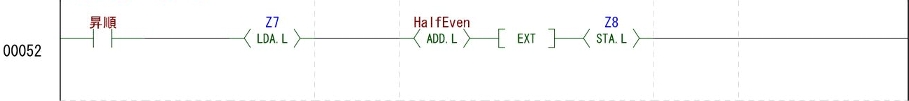

・[Z7](実際はレジスタ)と8(hex)の論理和をとる事で8〜15を作ります。昇順スイッチが真であれば [Z8]は 8 ⇒ 15 となります。

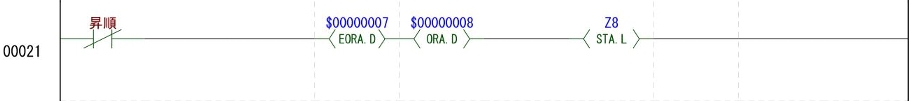

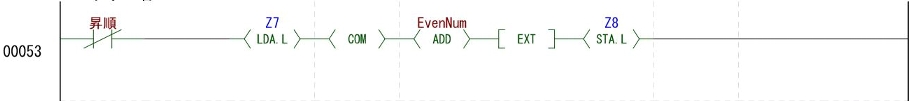

・[Z7](実際はレジスタ)と7(hex)〔0111(bin)〕の排他的論理和をとると、真であるビットが反転され、7 ⇒0と、逆行カウントします。

・逆行カウントと、8(hex)との論理和をとります。昇順スイッチが偽であれば、[Z8]は 15 ⇒ 8 となります。

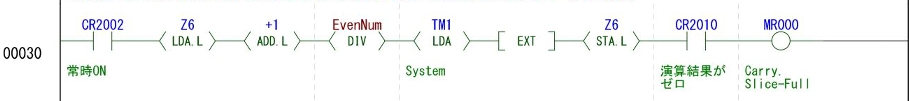

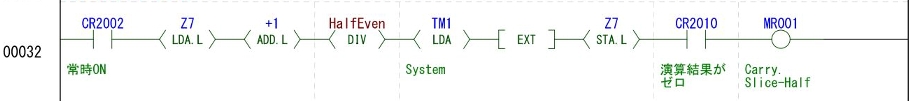

・リングカウンタ値は0〜(任意の偶数 − 1)

このルーチンを使うには [@MR001]をセットしてください。

・[Z6]に1を加えて、任意の偶数[EvenNum](ここでは16に設定)で割って、あまりを[Z6]に代入しています。

・定数[EvenNum]で割った余りは0〜( EvenNum- 1 )になるので、この場合、[Z6]は 0〜15 を繰り返します。

・この時、[Z6]が割り切れたなら[MR000]を立てます。

・同様に[Z7]に1を加えて、任意の偶数の半分[HalfEven](ここでは8)で割ったあまりを[Z7]に代入します。その結果[Z7]は 0〜7を繰り返します。

・[Z7]が割り切れたなら[MR001]を立てます。

・[Z7]は[Z6]が1巡する間、2回割り切れます。

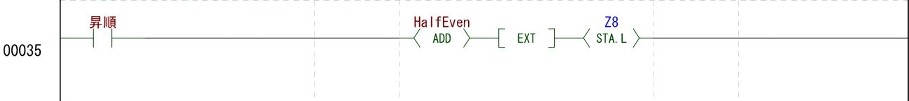

・[Z7](実際はレジスタ) に[HalfEven]を加えて、8〜15を作ります。昇順スイッチが真であれば[Z8]は 8 ⇒ 15となりま す。

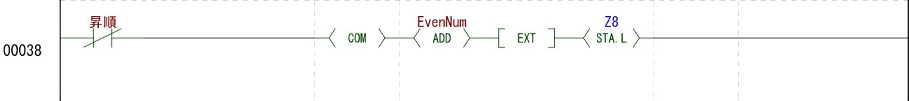

・[Z7](実際はレジスタ) を全ビット反転し、( 0 ⇒ 7 )を( −1 ⇒−8)に変換します。これに[EvenNum](16)を加えたものを[Z8]へ代入します。

・昇順スイッチが偽の時は、[Z8]は15⇒ 8となります。

・リングカウンタ値は0〜(任意の偶数 − 1)

このルーチンを使うには [@MR002]をセットしてください。

・[Z7]をインクリメントして、任意の偶数[EvenNum]との排他的論理和をとります。一致する(結果が0)と結果を[Z6]に代入し。一致フラグ [MR000]を立てます。

・この場合、[EnenNum]は16なので、[Z7]が16の時、[EvenNum] XOR [Z7]は0なので、[Z7]は 0〜15を繰り返しま す。

・同様に[Z7]をインクリメントして、任意の偶数の半分[HalfEven](ここでは8)との排他的論理和をとります。

・一致すると結果を[Z7]に代入します。その結果[Z7] は 0〜7を繰り返します。

・一致すれば、一致フラグ[MR001]を立てます。

・[Z7]は[Z6]が1巡する間、2回一致します。

・[Z7]に[HalfEven]を加えて、8〜15を作ります。昇順スイッチが真であれば [Z8]は 8 ⇒ 15となります。

・[Z7]を全ビット反転し、( 0 ⇒ 7 )を( −1 ⇒ −8 )に変換します。これに[EvenNum](16)を加えたものを[Z8]へ代入します。

・昇順スイッチが偽の時は、 [Z8]は 15⇒ 8と なります。

・PLCを起動すると、『2のn乗-1でマスクする』が選択され動作します。

・その後、[Full実行] / [Half実行] / [Step実行] の何れかを選択し、[@MR000] / [@MR001] / [@MR002]をセットするとインデックスレジスタがカウントされます。

・Full実行:[Z6]が 一巡したらカウント停止します。

・Half実行:[Z7]が 一巡したらカウント停止します。

・Step実行:1カウント 毎に停止します。

・昇順をセットすれば[Z8]が昇順カウント( 8 ⇒ 15 )、リセットすれば降順カウント( 15 ⇒ 8 )します。